[컴퓨터구조][Cache]

CPU의 구조에 대해서 배웠을 때, Instruction memory와 Data memory가 있었던 것을 기억하실 거에요. Instruction memory와 Data memory는 실제로 Cache memory를 사용합니다. Cache memory를 사용하는 이유는, 메모리

monkey-engineer.tistory.com

cache에 대해서 잘 모르신다면, 이전에 작성한 Cache 포스팅을 읽고 오시면 도움이 됩니다.

일반적으로 정보를 가지러 Main memory에 접근해야 하지만, 이 경우 overhead가 많이 듭니다.

그 이유는 메모리의 계층구조에서 알 수 있듯이 Main Meomory에 접근하기 위해서 많은 Clock이 소요되기 때문입니다.

이 문제를 해결하기 위해서 cache를 합니다. 여기서 만약 Multiprocessor구조라면

아래와 같이 구조는 각 Processor마다 아래에는 Data Cache라고 표현되어 있지만 L1 cache를 가지게 됩니다.

여기서 빠르게 Data에 접근하고 이용하려고 사용한 cache에 문제가 발생하게 됩니다.

예를 들어서, Processor가 2개라고 가정하고, X라는 주소에 10이 데이터 값이라면

Processor 0에서 X에 접근해서 20을 쓰고나서 Processor 1에서 이것을 읽는다면

Processor 0과 1의 X에 대한 값 중에 어떤 값이 유효한 값이라고 할 수 있을까요?

여기서 문제가 발생하게 되고, 이 문제를 Cache coherence라고 합니다.

역시 문제가 있으면 해결책이 존재하기 마련인데, 여기에 소프트웨어적인 방법과

하드웨어적인 방법이 있습니다. 여기서는 하드웨어적인 방법을 살펴보겠습니다.

하드웨어적인 방법에는 Directory-based protocols와 Snooping protocol이라는 방법이 존재합니다.

Directory-based protocols는 cache 와 memory가 공유하는 상태를 directory에 있는 block을 통해서 공유하는 방법입니다.

Snooping protocols는 bus의 read와 write에 대한 버스를 모니터하면서 신호가 생성되었을 때

이 신호를 받은 다른 cache들이 즉시 동일한 값으로 변경하거나 해당 데이터를 invalid하게 만드는 방법이 있습니다.

snooping protocols은 동일한 값을 변경(update)하거나 invalid하기 위해서 사용하는 MSI, MESI, MOESI protocol이 있습니다.

MSI, MESI, MOESI를 시작하기 전에 cache coherence protocol에서 초기화 상태는 Invalid입니다.

그 이유는 캐시는 빈 상태에서 시작하므로 데이터를 보유하고 있지 않고, 데이터를 로드하거나 수정하기 전에는 다른 프로세서나

메모리에 대한 영향을 최소화하기 위해서 초기 상태는 Invalid 상태로 유지되게 됩니다.

MSI

MSI protocol은 snooping protocols의 방법에서 기본이 되는 방법입니다.

|

|

| 출처: https://en.wikipedia.org/wiki/MSI_protocol | |

MSI protocol은 세 가지 상태가 존재합니다. Invalid, Shared, Modified

Processor Request

· PrRd: 프로세서가 캐시 블록을 읽기 위해 요청.

· PrWr: 프로세서가 캐시 블록에 쓰기 위해 요청.

Bus Request

· BusRd: 프로세서 캐시에서 읽기 실패가 발생하면, 프로세서가 BusRd요청을 버스에 보내고 캐시 블록을 반환받기를 기대

· BusRdX: 프로세서 캐시에서 쓰기 실패가 발생하면, 프로세서가 BusRdX요청을 버스에 보내고 캐시 블록을 반환받으며

다른 프로세서의 캐시 블록을 무효화.

· BusUpgr: 프로세서 캐시에서 쓰기 성공이 발생하면, 프로세서가 BusUpgr요청을 버스에 보내 다른 프로세서의

캐시 블록을 무효화.

· Flush: 캐시 블록 전체를 메모리에 기록(Write-back)하라는 요청

Invalid 상태

· PrRd: BusRd 요청이 발생하고 상태가 Shared로 변경.

· PrWr: BusRdX 요청이 발생하고 상태가 Modified로 변경.

· BusRd, BusRdX, BusUpgr: 무효 상태의 블록은 그대로 Invalid 상태 유지.

Shared 상태

· PrRd: Shared 상태 유지

· PrWr: BusUpgr 요청이 발생하고 상태가 Modified로 변경

· BusRd: Shared 상태를 유지

· BusRdX 또는 BusUpgr: Invalid 상태로 전환

Modified 상태

· PrRd or PrWr: Modified 상태 유지

· BusRd: 캐시 블록이 bus로 flush되고 상태가 Shared로 변경

· BusRdX: 캐시 블록이 bus로 flush되고 상태가 Invalid로 변경

· BusUpgr: 불가능, Modified 상태는 한 프로세서만 독점적으로 가질 수 잇으므로 다른 프로세서의 shared 상태에서

BusUpgr이 발생할 수 없다.

MESI

MESI protocol은 MSI의 단점을 보완하기 위해서 만들어졌습니다. MSI의 단점은 아래와 같습니다.

· Memory access overhead & Bus transaction

MSI protocol에서는 프로세서가 읽기 전용 상태에서 데이터를 캐시에 보관하더라도 항상 데이터를 Shared 상태로 유지합니다.

이로 인해서 캐시에 저장된 데이터가 읽기 전용임에도 불구하고 읽기 요청(PrRd)시 다른 캐시와 메모리를 확인해야 하기 때문에

불필요하게 다른 캐시와 메모리에 접근해야 하고, Bus의 불필요한 발생이 성능을 저하하는 결과를 가져올 수 있습니다.

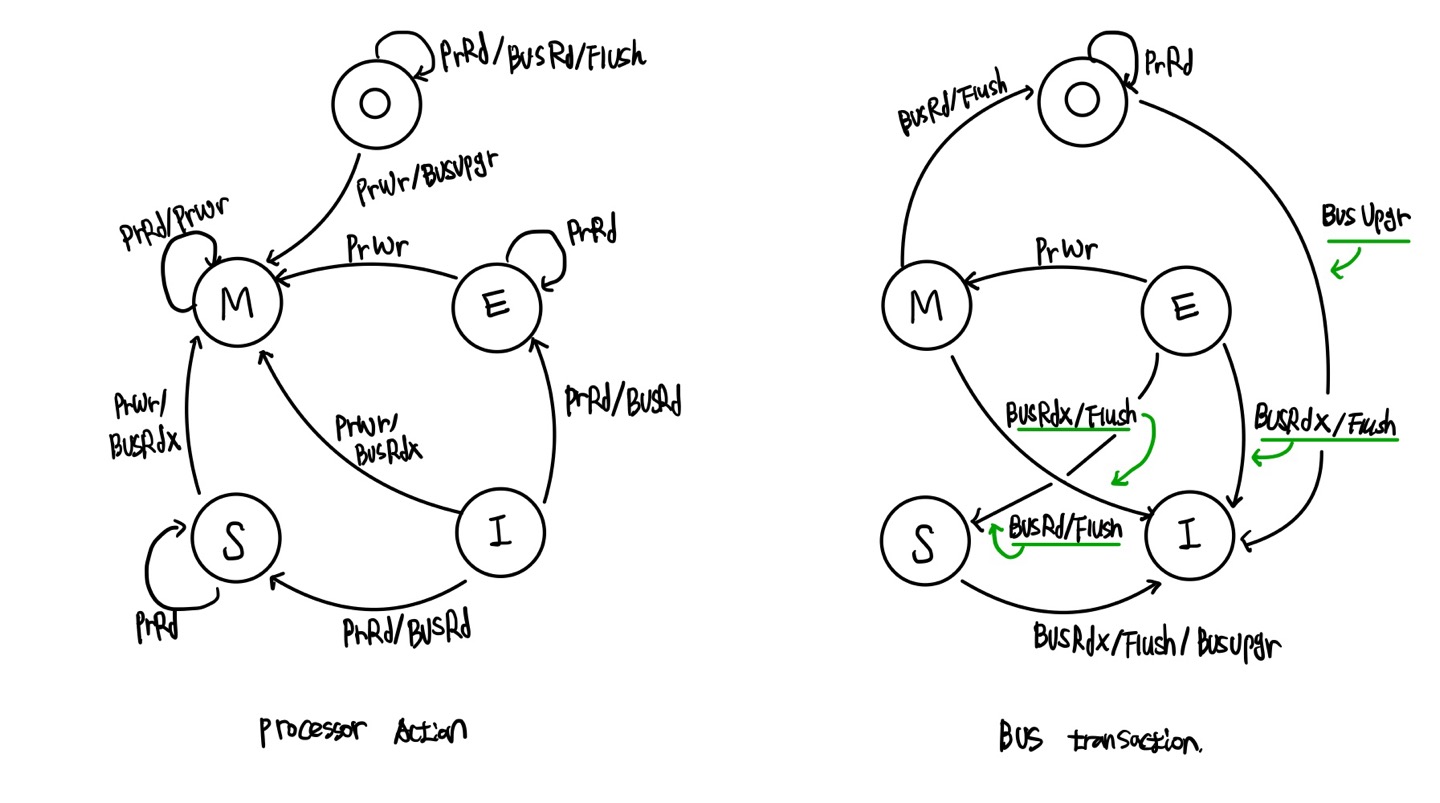

MESI protocol은 두 가지 자극에 따라서 상태가 전이되는데, 첫 번째는 PrRd, PrWr 요청이고,

두 번째는 Bus side request(버스 요청)입니다. 버스 요청은 캐시 블록이나 최신 데이터가 없는 다른 프로세서로부터 발생합니다.

Processor Request

· PrRd: 프로세서가 캐시 블록 읽기 요청

· PrWr: 프로세서가 캐시 블록에 쓰기 요청

Bus Request

· BusRd: 다른 프로세서가 요청한 캐시 블록에 대해 읽기 요청

· BusRdX: 다른 프로세서가 요청한 캐시 블록에 대해 쓰기 요청.(캐시 블록이 없는 상태에서 발생)

· BusUpgr: 다른 프로세서가 캐시 블록을 보유하고 있으면서 쓰기를 요청

· Flush: 다른 프로세서가 캐시 블록 전체를 메인 메모리에 기록

· FlushOpt: 다른 프로세서로 캐시 블록을 제공하기 위해 버스에 전체 캐시 블록을 게시(cache to cache 전송)

Snooping 동작

· 모든 캐시가 버스에서 발생하는 모든 트랜잭션을 모니터링

· 각 캐시는 물리적 메모리 블록의 공유 상태를 관리

· 상태는 프로토콜의 상태 다이어그램에 따라 전환

Invalid

· PrRd: BusRd 요청 발생

- 다른 캐시가 유효한 데이터가 있으면 Shared로 전환

- 없으면 Exclusive로 전환하고 메인 메모리에서 데이터 가져온다.

· PrWr: BusRdX요청 발생.

- 상태가 Modified로 전환

- 다른 캐시가 데이터 복사본을 가진 경우 무효화.

Shared

· PrRd: 캐시 hit, 상태 유지

· PrWr: BusUpgr 요청 발생. Modified로 전환, 다른 캐시는 Invalid로 전환.

Exclusive

· PrRd: 캐시 hit, 상태 유지

· PrWr: Modified로 전환. 버스 트랜잭션은 없음

Modified

· PrRd/PrWr: 캐시 hit, 상태 유지

· 다른 요청 시 데이터를 Flush하고 상태 전환

MOESI

MOESI protocol은 MESI protocol의 메모리 쓰기에 대한 단점을 보완하고자 개발되었습니다.

MESI protocol은 Modified 상태의 캐시 블록이 다른 프로세서에 의해 읽히는 경우에 해당 블록을 main memory에

기록한 후(clean, 클린) Shared 상태로 전환해야 합니다. 여기서 Main memory에 data를 쓰기 위한 overhead가 발생하기 때문에

이 문제를 해결하고자 Owned라는 상태를 추가하여 수정된 데이터가 여러 캐시에서 공유될 수 있음을 나타내기 때문에

Main memory의 데이터가 최신 상태가 아닐 수 있다는 의미를 내포하게 됩니다. Owned 상태에서는 해당 캐시가 메모리를

업데이트할 책임을 지게 됩니다. 만약 다른 프로세스가 해당 데이터를 요청할 때에는

memory에 기록하지 않고 직접 데이터를 제공합니다.

MESI구조에서 Owned가 추가된 것이 MOESI protocol입니다.

Modified

· 이 캐시는 캐리 라인의 유효한 복사본을 유일하게 가지고 있습니다. 캐시된 복사본은 자유롭게 추가 수정이 가능

Owned

· 이 캐시 라인은 시스템 내 여러 복사본 중 하나입니다. 이 캐시는 복사본을 수정할 권한이 없지만, main memory와 비교했을 때

수정된 상태(dirty, 더티)입니다. 이 캐시는 main memory를 나중에 업데이트를 해줘야 합니다.

· 캐시 라인은 다른 공유된 복사본을 무효화한 후 Modified 상태로 변경될 수 있습니다. Main memory에 수정된 것을 기록하고나서

Shared상태로 변경될 수도 있습니다.

· Owned 상태의 캐시 라인은 Snoop 요청을 통해서 cache to cache 통신을 하며, main memory의 오래된 복사본이 사용되지

않도록 보장합니다.

Exclusive

· 이 캐시는 라인의 유일한 복사본을 가지고 있지만, 해당 라인은 수정되지 않은 상태(clean, 클린)입니다. 데이터를 수정하면

Modified상태로 전환됩니다.

Shared

· 이 캐시 라인은 시스템 내 여러 복사본 중 하나입니다. 이 캐시는 복사본을 수정할 권한이 없습니다.

· MESI protocol과 달리 Shared 상태의 캐시 라인이 메모리와 비교해 dirty일 수 있습니다. 이 경우에는 다른 캐시 중 하나가

Owned 상태로 복사본을 가지고 있으며 main memory를 업데이트해야 합니다.

· 어떤 캐시도 해당 라인을 Owned 상태로 가지고 있지 않다면 main memory 복사본이 최신 상태라는 의미입니다.

· 캐시 라인은 Exclusive또는 Modified 상태로 전환하기 전에는 쓰기 작업이 불가능합니다. 이를 위해서 다른 모든 캐시 복사본을

무효화해야 합니다.

· 캐시 라인은 언제든 Invalid 상태로 폐기될 수 있습니다.

Invalid

· 이 블록은 유효하지 않으며 접근하려면 먼저 fetch(가져와야합니다.)해야 합니다.

Owned

· 캐시 라인이 여러 캐시에 존재하면서 main memory와 비교해 dirty일 때 하나의 캐시가 main memory 업데이트를 책임집니다.

· 이를 통해 불필요한 메모리 쓰기 작업을 줄이고 시스템 성능을 최적화할 수 있게 됩니다.

지금까지 cache coherence에 대해서 살펴봤습니다. state diagram과 함께 설명들을 쫓아가보시면 이해가 훨씬 쉽습니다.

이로써 cache에 대한 대단원이 막을 내린 것 같습니다. 물론 더 있을 수 있지만, 아무래도 학습한 것을 기본으로 하기 때문에

다음에 더 심화해서 배우는게 있다면 또 추가적으로 글을 올리도록 하겠습니다.

글 읽어주셔서 감사합니다.

'전자전기공학 > 컴퓨터구조' 카테고리의 다른 글

| [컴퓨터 구조][Out of order] (2) | 2024.11.15 |

|---|---|

| [컴퓨터 구조][Parallel] (0) | 2024.11.13 |

| [컴퓨터구조][virtual memory] (10) | 2024.10.27 |

| [컴퓨터구조][cache#2] (0) | 2024.10.25 |

| [컴퓨터구조][Cache] (0) | 2024.10.16 |