CPU의 구조에 대해서 배웠을 때, Instruction memory와 Data memory가 있었던 것을 기억하실 거에요.

Instruction memory와 Data memory는 실제로 Cache memory를 사용합니다.

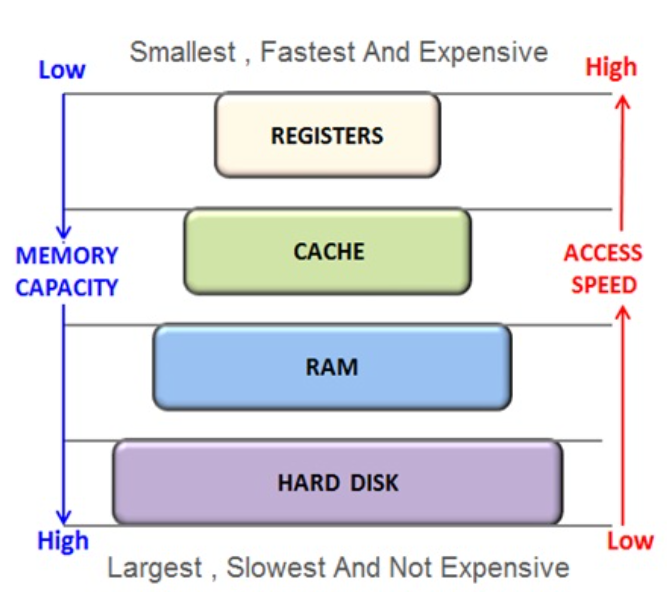

Cache memory를 사용하는 이유는, 메모리 계층 구조를 보시면 알 수 있습니다.

맨 위를 기준으로 Register가 있고, 아래로 가면서 Memory의 크기는 커지지만 Access 속도가 느려집니다.

이런 이유로 Cache memory를 이용해 RAM(주로 memory라고 하면 RAM을 지칭합니다.)의 일부 자주 사용되는 데이터를

Cache에 두고 빠르게 접근하고 사용하기 위해서 입니다. 즉, CPU의 효율을 올리기 위해서 사용한다고 볼 수 있습니다.

그렇다면 RAM(or main memory or memory)에 있는 데이터를 어떤 기준으로 cache에 가져오게 될까요?

캐시와 메모리의 mapping은 메인 메모리의 데이터가 cache의 어디에 위치할지 정하는 규칙과 알고리즘 입니다.

mapping에는 cache에 어떤 방식으로 mapping할지에 따라서 Direct mapping과 associative cache로 나뉩니다.

Direct Mapping

Direct Mapping은 cache와 memory를 mapping하는 가장 간단한 방법입니다.

cache의 block은 주로 2의 거듭제곱으로 결정됩니다. 그 이유는 아래에 나올 mapping 위치는

modulo계산으로 결정되기 때문에 2의 거듭제곱으로 설정을 하게 됩니다.

cache에 mapping되는 위치는 아래의 공식에 의해서 결정됩니다.

$\text{Block number} \; \text{modulo} \; \text{(Number of blocks in the cache)}$

cache의 mapping 위치가 결정된다면, 해당 block에 데이터를 작성해야 하는데, 데이터의 구조는 어떻게 될까요?

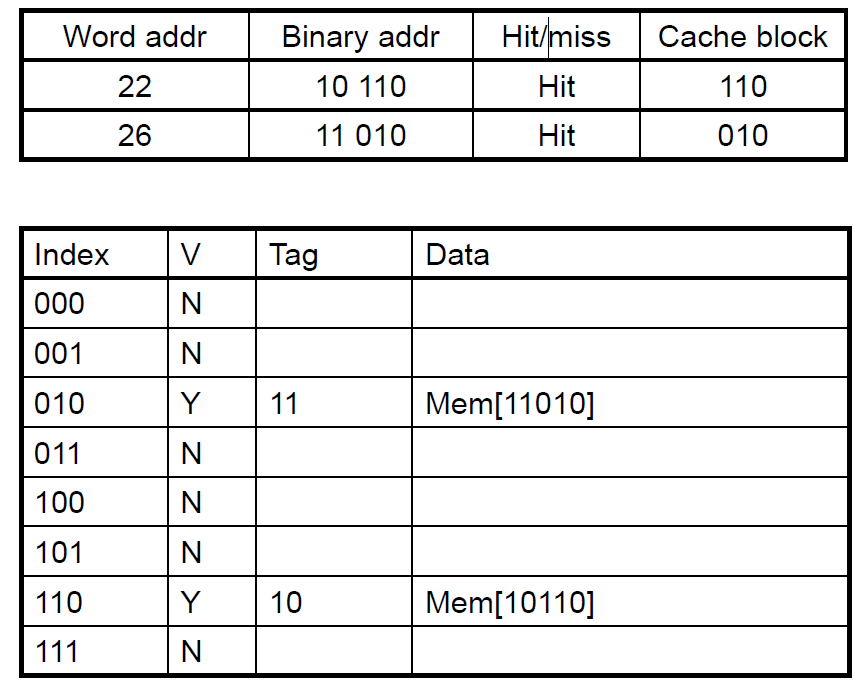

위를 보면 총 8개의 index가 표현되어 있습니다. 여기서 index와 Valid bits(V) 그리고 Tag가 들어가게 됩니다.

예를 들어서 22 word address가 있다면, 10110으로 표현이 가능하고, 하위 3비트는 index 그리고 상위 2비트는 Tag가 됩니다.

여기서 cache에 정보가 쓰이게 되면 valid bit은 당연히 1(Y)가 됩니다.

아래 그림으로 감을 잡아보시면 될 것 같습니다.

위에서 봤던 것 처럼 mapping의 방법은 두 가지 입니다. 두 가지라는 것에서 대충 감을 잡으셨겠지만, 장단점이 존재하기 때문에

trade off를 감안해서 여러가지 방법이 사용됩니다.

우선 장단점을 알아보고 다른 방법을 알아보기 전에 장단점을 알 수 있는 용어를 살펴보겠습니다.

첫 번째로, Temporal Locality은 최근에 접근한 데이터나 명령어가 가까운 미래에도 재사용될 가능성이 높다는 성질입니다.

두 번째로, Spatial Locality는 최근 접근한 데이터의 주변 데이터가 곧 사용될 가능성이 높다는 성질입니다.

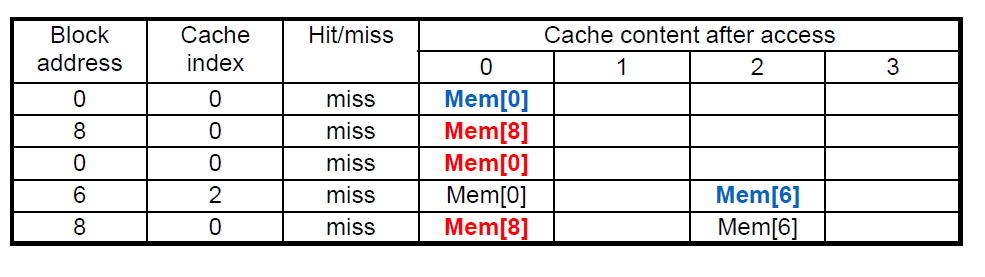

그렇다면 Direct Mapping의 단점은 무엇일까요?

첫 번째로, 여러 메모리 블록이 같은 캐시 블록을 공유해야 하는 경우가 많게 됩니다.

예를 들어서 00000, 10000, 20000이 있는 경우 같은 cache block에 매핑될 경우 접근 할 때마다

이전 블록이 덮어써지면서 충돌이 발생하게 됩니다. 이는 캐시 효율을 떨어트리고 전체적인 성능을 저하됩니다.

두 번째로, 캐시의 크기가 고정된 경우에 블록에 저장되는 크기가 커질수록 저장할 수 있는 블록이 수가 줄어듭니다.

만약 캐시의 총 크기가 256KB일 때,

$\frac{256*1024}{32}=8192block$

$\frac{256*1024}{64}=4096block$

결국 block의 크기는 줄어들게 됩니다.

이제 해당 단점을 보완하기 위한 다른 방법이 있는데, Associative cache에 대해서 알아보도록 하겠습니다.

Associative Cache

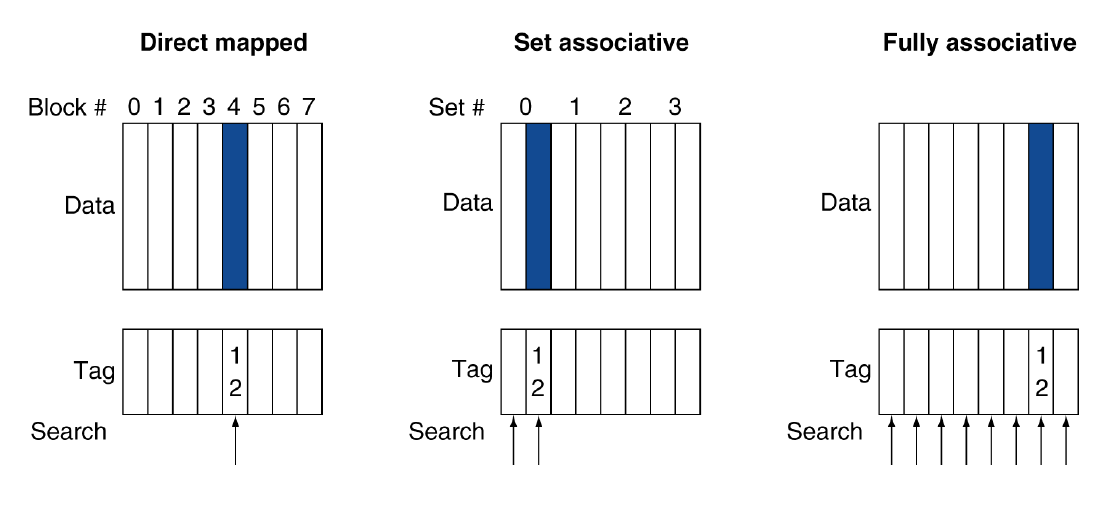

Associate Cache에는 fully associative 와 n-way set associative가 있습니다.

fully associative

fully associative는 direct mapping의 충돌을 해결하기 위해서 사용됩니다.

fully associative는 메모리 블록을 cache의 어느 위치에든 저장할 수 있기 때문에 근본적인 충돌 문제를 해결할 수 있습니다.

하지만 fully associate를 사용하게 된다면, 블록 어디든 위치할 수 있기 때문에 cache hit인지 miss인지를 확인하기 위해서

모든 block들과 comparator를 이용해서 비교해줘야 하기 때문에 면적이 늘어나고 power consumption이나 speed면에서도

단점을 가지게 되기 때문에 fully associative와 direct mapping의 장점을 가지고 n-way associative를 사용하게 됩니다.

n-way associative

n-way associative는 여러가지 set으로 구분해서 cache를 여러 블록으로 구성하고,

set에는 여러 way(block)이 존재하게 됩니다.

위의 그림을 참고해서, n-way associative는 n개의 comparator만 있으면 되기 때문에

fully associative의 단점을 보완하게 되고, 각 set당 각 n-way의 n만큼 block을 가지고 있기 때문에

Direct mapping이 가지고 있던 충돌에 대한 단점 또한 보완하게 됩니다.

아래 그림을 보면서 한번 단점과 장점을 생각해보시면, 이해가 쉬울 것 입니다.

마지막으로, n-way associative는 n의 크기가 클수록 miss rate가 줄어들게 됩니다.

그 이유로, 특정 메모리 주소는 하나의 Set에만 매핑되지만, 그 Set 안의 N개의 way 중에

어느 블록에든 저장될 수 있기 때문에, Direct mapping의 충돌을 해결한다고 했던 만큼

miss rate가 줄어들게 되고, 덮어쓰기 되지 않고 set안의 block이 커질수록 많은 데이터를 set으로 구분된

mapping안에서 가질 수 있게 되기 때문입니다.

하지만 모든 것은 trade off인 것 같습니다. n-way가 커지면 hit rate가 올라가지만 way의 수가 너무 많게 된다면,

탐색 시간과 하드웨어 비용이 증가할 수 있기 때문입니다.

또한, 대부분 system을 검증할 때 사용하는 SPEC2000을 가지고 검증을 했을 때,

4-way associative와 8-way associative에서부터 큰 성능 향상이 이뤄지지 않는다고

검증 결과가 나오고 나서부터 현대에는 4-way associate와 8-way associate를 가장 많이 사용한다고 합니다.

다음에는 cache에 대한 보충내용이 있다면 추가하고나서 virtual machine과 virtual memory에 대해서 알아보도록 하겠습니다.

감사합니다.

'전자전기공학 > 컴퓨터구조' 카테고리의 다른 글

| [컴퓨터구조][virtual memory] (10) | 2024.10.27 |

|---|---|

| [컴퓨터구조][cache#2] (0) | 2024.10.25 |

| [컴퓨터구조][Hazards #2 Control Hazard] (0) | 2024.10.13 |

| [컴퓨터구조][Hazards #1 Data Hazard] (0) | 2024.10.11 |

| [컴퓨터구조][CPU#3 Pipelining기본] (1) | 2024.10.02 |