안녕하세요, 지난 시간에 이어서 CPU의 Pipelining(파이프라이닝)에 대해서 배워보도록 하겠습니다.

우선 파이프라이닝에 대한 개념을 우선 배워보도록 하겠습니다.

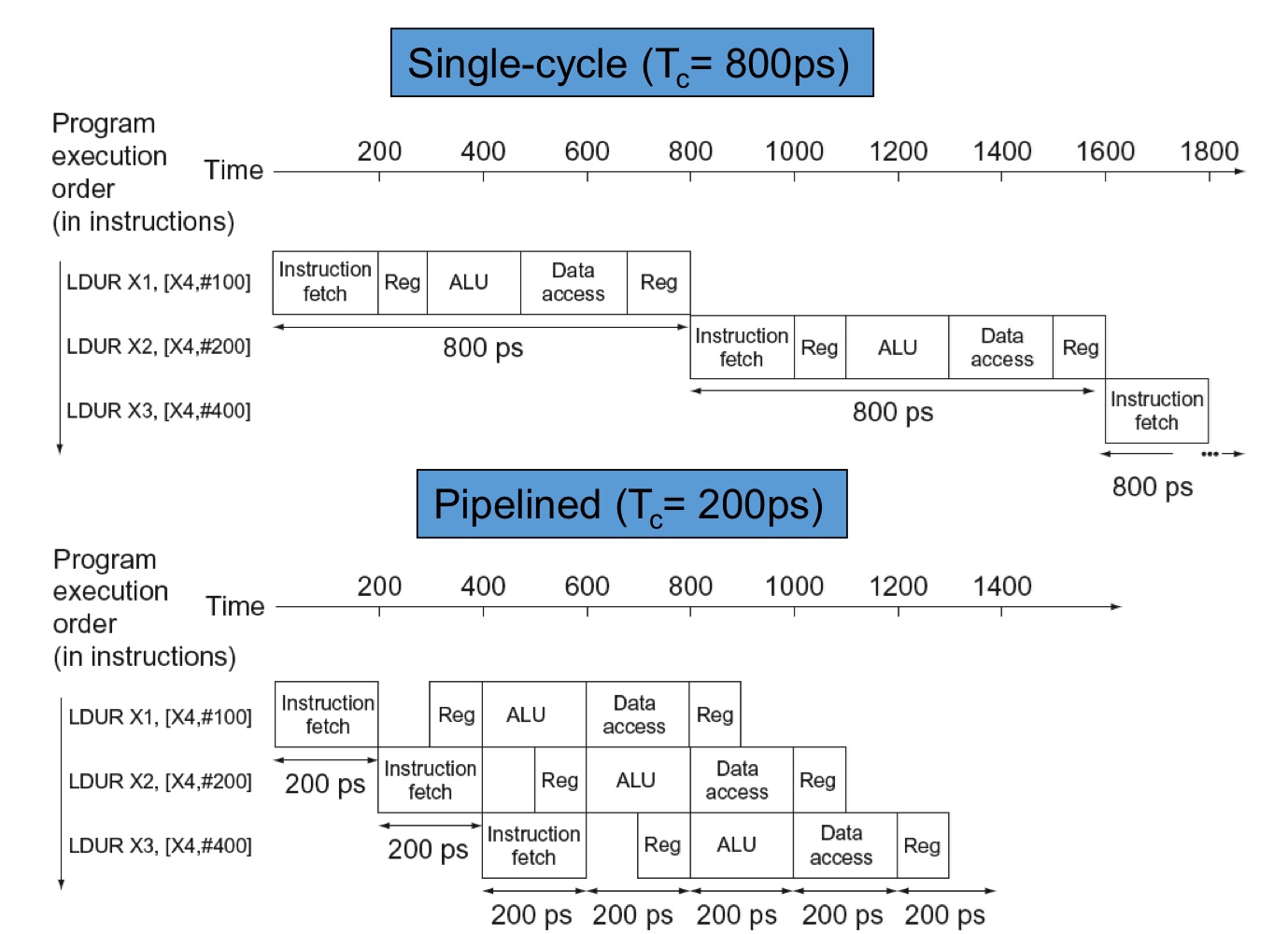

아래의 그림은 파이프라이닝에 대한 예시 그림입니다.

파이프라이닝은 작업을 여러 단계로 나누고, 각 단계가 동시에 실행되도록 하는 방식입니다.

쉽게 이야기해서 쉬는 곳이 없도록 모두 일을 지속적으로 실행할 수 있도록 하는 것 입니다.

여기서 파이프라이닝을 Latency(지연 시간)과 Throughput(처리량)을 생각하면 개선 사항을 쉽게 알 수 있습니다.

Latency는 하나의 작업을 완료하는 데 걸리는 시간입니다. 예를 들어서 아래의 그림처럼 하나의 작업을

완료하는 데 걸리는 시간을 의미합니다.

그리고 Throughput은 일정 시간 동안 얼마나 많은 작업을 완료했는지를 측정하는 개념입니다.

예를 들어서 1초 동안 5개의 작업을 완료했다면 그 시간 동안의 Throughput은 5입니다.

Throughput이 높아질수록 같은 시간 동안 더 많은 작업을 처리할 수 있다는 것은 당연한 사실일 겁니다.

위의 자료를 보면, 모든 파이프라이닝은 Clock에 맞춰서 수행을 하기 때문에 모든 작업은 200ps을 갖습니다.

latency 측면에서 보자면 파이프라이닝된 것이 더 느리지만, Throughput의 입장에서 보자면

오히려 성능이 훨씬 좋다고 볼 수 있습니다.

이제 CPU의 Pipelining에 대해서 본격적으로 배워볼 것 인데, Pipelining을 instruction execution을 기준으로 적용할 수 있습니다.

CPU에서 기본적으로 아래의 5가지 단계로 구분하여 적용할 계획입니다.

1. IF: Instruction fetch from memory(RAM)

2. ID: Instruction decode & register read

3. EX: Execute operation or calculate address

4. MEM: Access memory operand

5. WB: Write result back to register

위의 단계에는 Register가 필요합니다. 왜냐하면 Single Cycle은 정보를 저장해두고 기억하는 register가 없기 때문에

Combinational logic circuit이라고 볼 수 있지만,

Pipelining을 하게되면 각 단계에 register가 있고 정보를 저장한 것을 기반으로

다음 단계를 처리하기 때문에 Sequntial logic circuit이라고 할 수 있습니다.

따라서 각 단계의 정보를 저장해뒀다가 저장된 정보를 이용해서 다음 단계에 또 다른 기능을 수행하기 때문입니다.

우선 위에서 헷갈릴 수도 있기 때문에 파이프라이닝을 적용해도 Single Cycle은 맞습니다.

단지 Single Cycle에 파이프라이닝이 적용된 것인지 아닌지에 따라서 달라지는 것이라고 생각하시면 될 것 같아요.

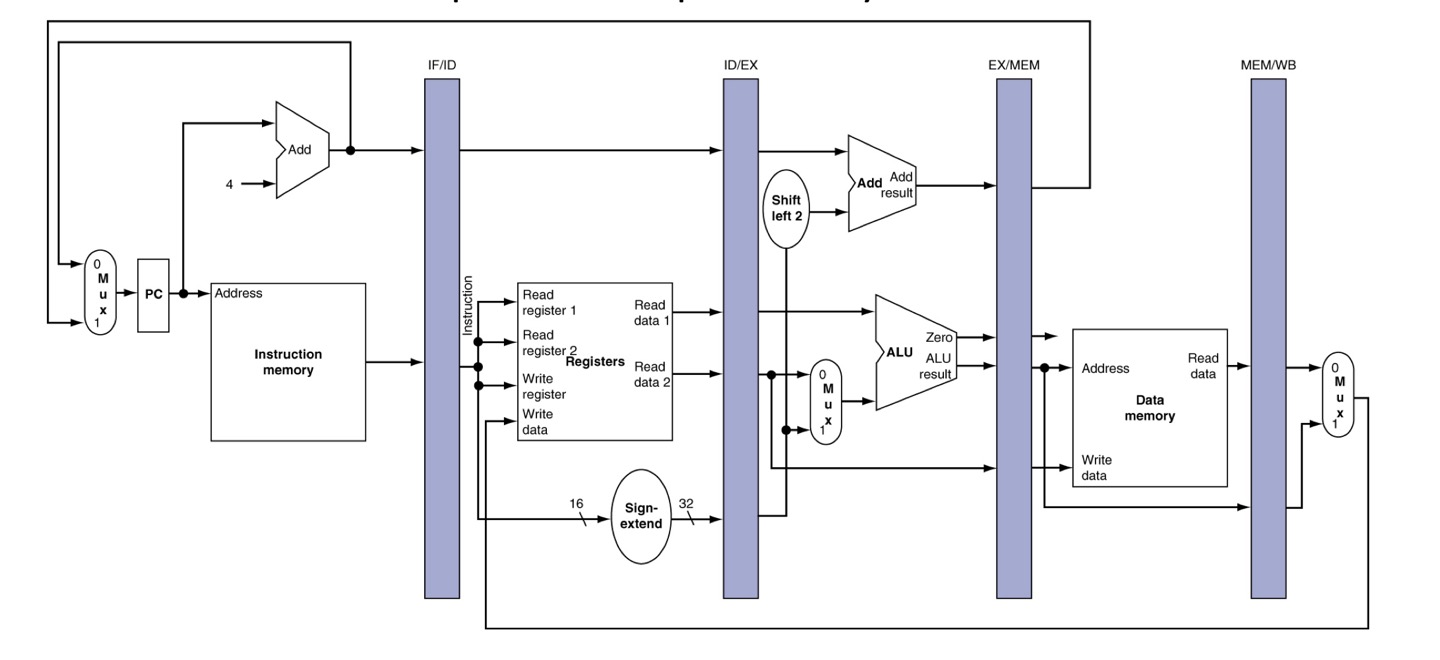

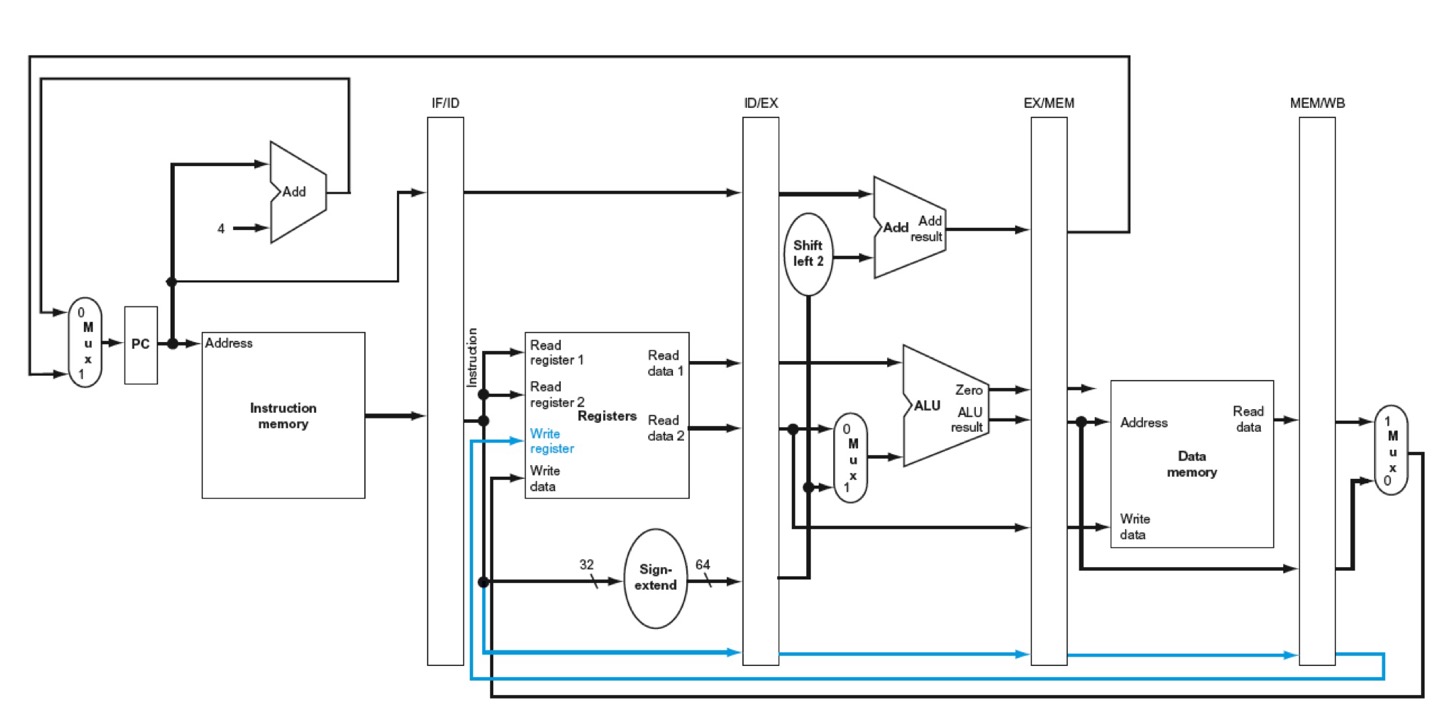

아래는 위에서 말했던 다섯 단계로 register를 이용해서 파이프라이닝을 적용한 회로입니다.

이제 위의 회로에서 Lode/ Store 명령어가 실행되는 과정을 살펴보면서 파이프라이닝된 회로를 살펴보겠습니다.

자료에서 보면 LDUR명령어를 수행하는 과정중에 제일 첫 단계에 해당하는 IF단계입니다.

IF단계는 위에서도 설명이 있듯이 Instruction Fetch 단계입니다.

IF 단계는 Instruction memory에서 instruction을 가져와서 register에 저장하는 역할을 수행합니다.

위에서도 그렇고 앞으로 파란색 부분으로 칠해진 부분이 수행되는 곳이라고 생각하시면 됩니다.

여기서는 ID단계로 Instruction Decode단계입니다.

Opcode에 따라 앞으로 수행에 필요한 control signal을 생성 및 수행에 필요한 값을 register file에서 읽어와서

ID/EX register에 저장해둡니다. 여기 위에서는 Rn을 읽어와야 하는 것은 당연히 아시겠죠?

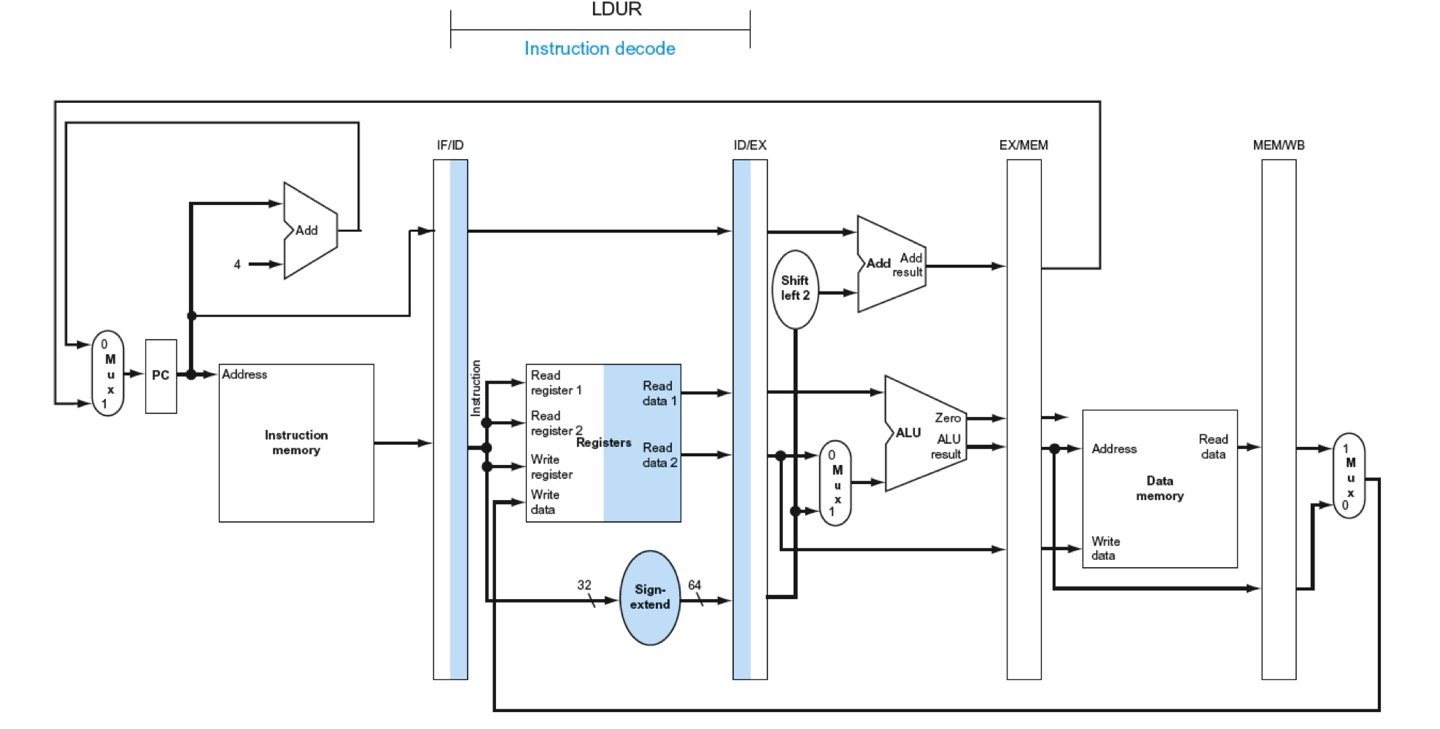

해당 단계는 EX단계로 Execution하는 단계입니다.

EX단계에서는 이전 단계에서 저장해둔 ID/EX register의 값 또는 immediate value간의 연산을 수행합니다.

해당 단계에서는 MEM단계로 memory로 부터 address에 맞는 data를 읽어서 MEM/WB에 저장하는 단계입니다.

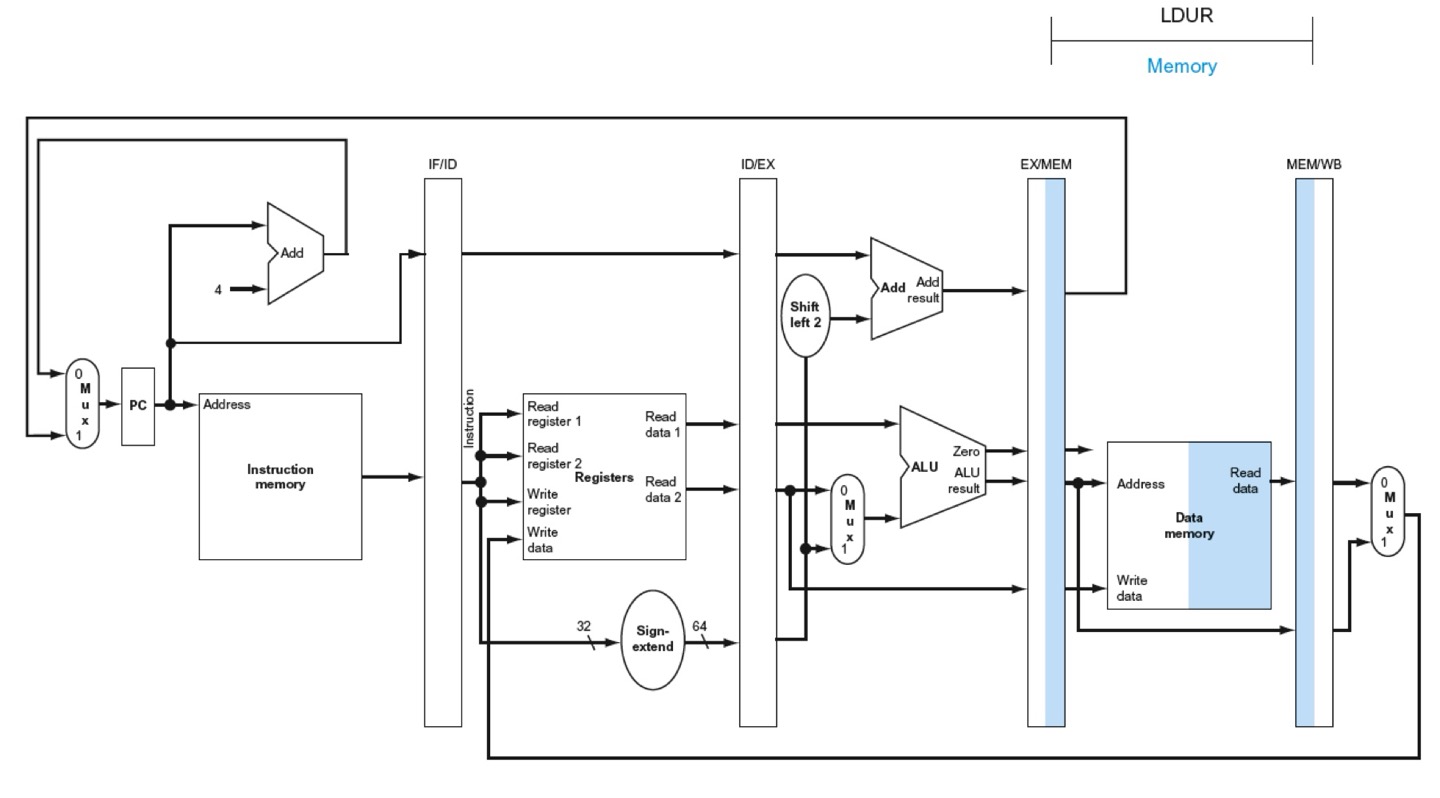

이제 마지막으로 WB단계로 Write Back 단계입니다. Write Back단계는 memory에서 읽어온 결과를

register에 작성하는 단계입니다.

하지만 자료를 보면 빨간색 동그라미가 있는데 왜 빨간색으로 동그라미를 해놓은 것일까요?

이유는 파이프라이닝의 수행과정을 기억해보시면 간단하게 이해할 수 있습니다.

파이프라이닝은 병렬로 명령어들을 수행하는 것 입니다.

예를 들어서 LDUR 명령어가 WB단계까지 왔다는 것은 ADD, SUB 또는 STUR등 여러가지 명령어가 이전 단계에서

수행중이라는 것을 아실 수 있습니다.

더 자세히 이야기해서,

LDUR → WB단계 수행중

ADD → MEM단계 수행중

SUB → EX단계 수행중

STUR → ID 단계 수행중

LDUR → IF단계 수행중

이렇게 LDUR이 WB단계에서 수행과정중에 4가지 명령어가 추가적으로 이전 단계들에서 수행중이라는 것 입니다.

그렇다면 회로를 봤을 때 Register(ID단계에서의 Register)에 Write register는 LDUR에서 지정해놓은 주소가 아니라,

현재 STUR에서 지정해 놓은 주소에 WB단계에서 수행중인 LDUR의 결과가 씌여지게 되는 것입니다.

그러면 잘못된 주소에 LDUR의 수행결과가 들어가기 때문에 안될 것이라는 것은 다들 이해하시겠죠?

따라서 기존 WB에서 수행중인 LDUR가 지정해 놓은 주소 또한 파이프라이닝 register에 저장되어서 명령어와 함께

진행되다가, WB단계가 끝났을 때 해당 주소가 Register File에 같이 넘어가야 합니다.

해당 회로를 그려보면 아래와 같겠죠?

여기서 추가적으로 Store(STUR)명령어의 경우에는 MEM단계에서 수행이 끝나게 됩니다.

왜냐하면 store은 메모리에 레지스터의 값을 기록하고 끝나기 때문입니다.

하지만 여기서 파이프라이닝은 모두 수행해야 하기 때문에 WB까지 수행을 하고 끝나야 합니다.

그럼 store은 WB단계에서 무엇을 수행하고 끝나는 것일까요?

실제로 WB단계에서 아무것도 수행하지 않습니다. 그러니까 어떻게 아무것도 수행하지 않고 끝내는지 궁금하실 수 있는데,

Register File에 값을 쓰는 동작이 없기 때문에 Write Reg 신호가 0으로 설정됩니다.

0으로 설정되면 WB단계에서는 레지스터에 값을 쓰지 않게 되며 그 단계는 Register File에 아무것도 작성(수행)하지 않고

해당 단계는 종료하게 되는 것 입니다.

여기까지 파이프라이닝의 기본 지식과 CPU에서 파이프라이닝이 어떻게 적용되는지 기본적인 부분을 살펴봤습니다.

파이프라이닝은 설계자에 따라서 파이프라이닝을 적용하는 부분들이 달라질 수 있으며 위에서 설명된 것은 기본적인 사항입니다.

바로 위에서 보면, 파이프라이닝은 각 단계를 수행하고 그 값을 저장했다가 다음 단계에서 사용하며 여러가지 명령어가

병렬적으로 수행되기 때문에 문제가 생기기도 합니다.

그런 문제들을 여기서는 Hazard라고 하며 Sturcture hazard, Data hazard, Control hazard가 있습니다.

해당 hazard들을 없애고자 설계에서 달라지는 부분도 있으며 이해하기 복잡한 부분도 생기기도 합니다.

다음에는 각 hazard에 대해서 살펴보고 회로가 어떻게 바뀌게 되는지 살펴보도록 하겠습니다.

감사합니다.

'전자전기공학 > 컴퓨터구조' 카테고리의 다른 글

| [컴퓨터구조][Hazards #2 Control Hazard] (0) | 2024.10.13 |

|---|---|

| [컴퓨터구조][Hazards #1 Data Hazard] (0) | 2024.10.11 |

| [컴퓨터구조][CPU#2 Single Cycle CPU, Dual Port SRAM] (4) | 2024.10.01 |

| [컴퓨터구조][CPU의 기본역할 및 성능] (0) | 2024.09.27 |

| [컴퓨터구조][Arithmetic/Floating point] (10) | 2024.09.25 |