· 목차

- Instruction Fetch

- R-Format Instructions

- Load/Store Instruction(D-format Instruction)

- Branch Instruction (CBZ)

- Dual Port SRAM

안녕하세요, 이번 시간에는 CPU의 각 파트가 어떻게 작동되는 것인지 살펴보고 난 이후에

Dual Port SRAM의 Transistor level에서의 구조에 대해서 살펴보고 넘어가도록 하겠습니다.

Instruction Fetch

위는 CPU에서 Instruction Fetch 파트만 따로 떼어온 것 입니다.

Instruction Fetch에서 보이는 것중 하나로 Arm Architecture에서 기존에 설명한 것과 같이

PC(Program Counter)는 명령어를 수행할 때 마다 PC + 4 만큼 증가한다는 것 입니다.

PC가 4씩 증가하는 이유는 모든 Instruction이 32bit이기 때문입니다.

그리고 위에서 PC + 4(초기에는 PC의 초기값)의 값이 Instruction memory의 Read address에 들어가는 것을 보실 수 있습니다.

또한 Read Address에 들어가는 값들은 Assembly 언어로 작성된 코드가 컴파일될 때 결정됩니다.

R-Format Instructions

위의 구조는 R-Format Instructions를 수행할 때 사용되는 CPU의 부분만 떼어온 것 입니다.

뒤에서 보겠지만, Read register1은 Instruction의 [9-5], Read register2은 Instruction의 [20-16] 혹은 Instruction의 [4-0]에서

5bit을 읽어오게 됩니다.

왜냐하면 이전에 R,D,I - format Instruction을 살펴보면 Rm(second register source operand)는

[16-20]에 해당하는 bit을 읽어옵니다.

마찬가지로 Rn과 Rd를 어디서 읽어오는지 확인해보면 왜 5bit씩 Instructon address에서 해당 bit을 읽어오는지 아실 수 있습니다.

그렇다면 [20-16]혹은 Instruction의 [4-0]에서 읽어온다는 것은 무슨 말일까요?

여기서 Instruction [4-0]이 되는 이유는 나중에 배우겠지만, I-format Instruction의 경우에는

Rt(데이터를 읽거나 쓸 레지스터를 지정하는 필드)가 [4-0]에 해당하기 때문에 R인지 I format인지에 따라서 다르게 됩니다.

Load/Store Instruction(D-format Instruction)

위의 구조는 D-format Instruction에 해당하는 파트입니다.

Sign extenstion unit이 필요한 이유는 이전에 이야기 했던 것 처럼,

Load의 경우에는 $R_{t} \; ← \; mem[R_{n}+address]$

Store의 경우에는 $R_{t} \; ← \; mem[R_{n}+address]$

여기서 $R_{n}$와 $R_{n}$ 이 무엇을 가르키는지에 따라서 다를 것이라는 것은 알고 계실 거라고 생각해요.

위와 같기 때문에 $R_{n}$과 address를 더하기 위해서 32bit의 address를 64bit로 확장시켜줄 필요가 있습니다.

그 이유는 이전에 설명했던 것과 같이 32bit과 64bit을 더할 수 없기 때문입니다.

여기서 Sign Extention을 하는 이유는 주소값은 양수지만 메모리의 특정 위치를 기준으로 음수 오프셋도 있을 수 있기 때문에

부호를 유지하면서 확장해야 합니다.

그리고 D-format Instruction의 경우 Write data와 Read data 포트를 이용해서 읽거나 쓰게 됩니다.

마지막으로 Store와 Load를 상기시키자면,

Load는 memory에서 값을 읽어와서 register의 값을 업데이트 하는 것 입니다.

Store은 register의 값을 memory에 쓰는 것 입니다.

Branch Instruction (CBZ)

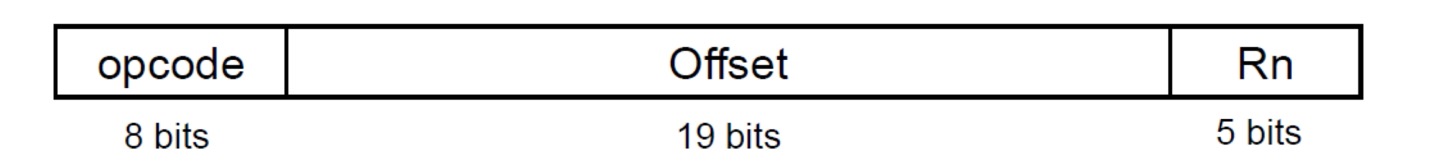

위는 Branch Instruction파트와 더불어 Instruction의 address구조 입니다.

여기서 Rn은 PC+ Offset*4를 통해서 분기할 수 있습니다.

이 부분은 딱히 어려운 것이 없기 때문에 바로 넘어가도록 하겠습니다.

결국 위에서 말한 파트들과 함께 Control signal Data path를 그려보면 아래와 같습니다.

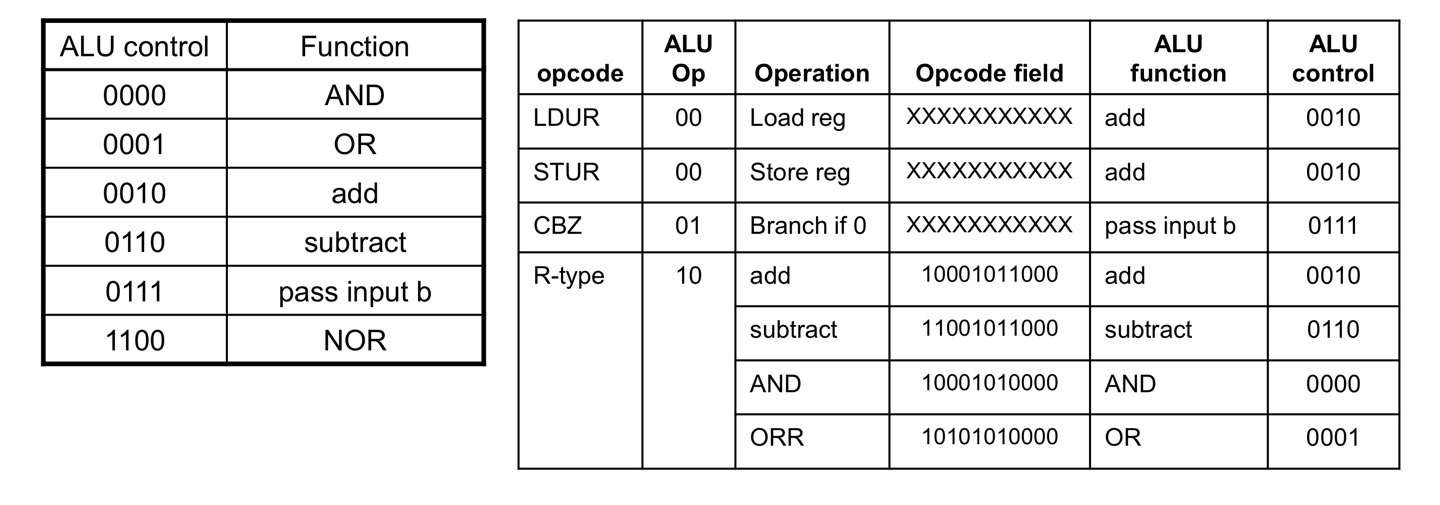

마지막으로 위에서 ALU operation을 위한 ALU Control signal은 아래와 같은 형식을 갖추고 있습니다.

결국에 모든 Consrol signal을 가지고 있는 Control unit을 함께 구조를 그려보면 지난 시간에 봤던 아래와 같은 구조가 됩니다.

Dual Port SRAM

저희가 흔히 알고 있는 SRAM을 Transistor level에서 회로를 그려보면 위와 같습니다.

위의 CPU 하드웨어 구성을 보면 Registers라고 되어있는 것을 볼 수 있는데, register file이라고 불립니다.

register file은 CPU에서 데이터를 빠르게 읽고 쓰기 위한 공간이므로, 여러 데이터를 동시에 읽거나

쓰기 위한 공간이므로 여러 데이터를 동시에 읽거나 쓸 수 있도록 향상되어야 하기 때문에

Dual port SRAM이라는 구조를 사용하게 됩니다.

Dual port SRAM은 아래의 구조와 같습니다.

지금까지 Single Cycle CPU에 대해서 살펴봤습니다. 이것 이후에 속도향상을 위해서

Pipelining을 사용하게 되는데, Pipelining에는 여러가지 조심해야 할 부분도 있고,

하드웨어 구조가 달라지게 됩니다.

해당 내용은 다음 시간에 살펴보도록 하겠습니다.

감사합니다.

'전자전기공학 > 컴퓨터구조' 카테고리의 다른 글

| [컴퓨터구조][Hazards #1 Data Hazard] (0) | 2024.10.11 |

|---|---|

| [컴퓨터구조][CPU#3 Pipelining기본] (1) | 2024.10.02 |

| [컴퓨터구조][CPU의 기본역할 및 성능] (0) | 2024.09.27 |

| [컴퓨터구조][Arithmetic/Floating point] (10) | 2024.09.25 |

| [컴퓨터구조][Procedure] (2) | 2024.09.24 |