Virtual memory는 Base and Limit Register를 사용할 때 발생하는 문제는 Program이 Main memory보다 크게 된다면

프로그램을 돌릴 수 없다는 문제가 발생하게 됩니다.

이는 Base and Limit Register를 돌리려면 전체가 다 올라와야 한다는 것 때문입니다.

그래서 이 문제를 해결해주기 위해서 Overlay방법과 Paging방법이 있습니다.

Overlay방법은 OS가 하는게 아니라 프로그래밍을 할 때, 프로그램을 로딩할 때 A만 로딩을하고 난 이후에 A프로그램이

전부 실행되고 나면 프로그램 B가 프로그램 A의 영역을 적재하는 방식으로 프로그래밍을 해줘야 합니다.

쉽게 말해서, 프로그램P가 있을 때 P의 Overlay section(A, B, C)으로 나뉘어져 있으면 A가 실행 중에 섹션 B가 필요해지면

A를 메모리에서 내려놓고 B를 로드하는 방식으로 사용되는 것 입니다.

Overlay는 다루기 복잡하기 때문에 이를 위해서 Paging이라는 방법이 나오게 됩니다.

Paging은 프로그램의 모든 주소공간이 메모리에 다 올라올 필요가 없기 때문에 고정된 크기의 블록(페이지)로 나누어

가상 메모리와 물리적 메모리 사이에서 관리하게 됩니다. Paging은 OS와 Hardware가 함께 관리해주는 것입니다.

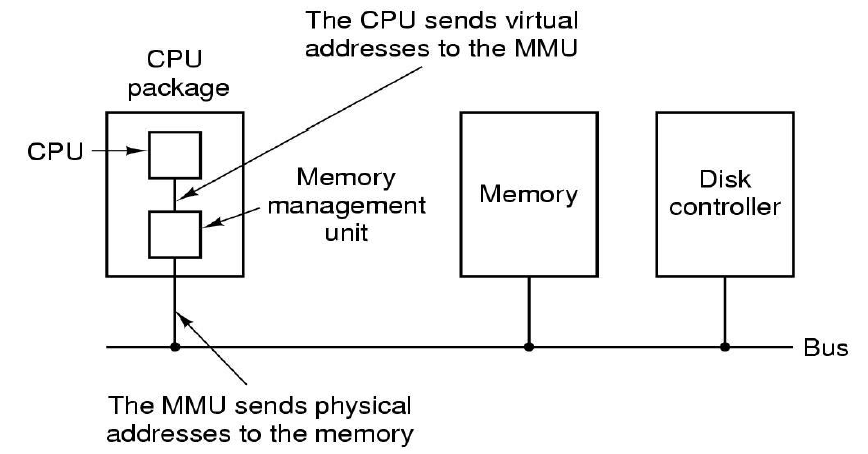

위의 그림에서 Paging과 연관된 것 뿐만 아니라 MMU에는 Base and Limit register방식이 사용되거나 Paging 기법이 Hardware기법이 들어갈 수 있습니다. MMU에서는 Virtual address를 변환시켜서 Physical address를 memory bus에 올리게 됩니다.

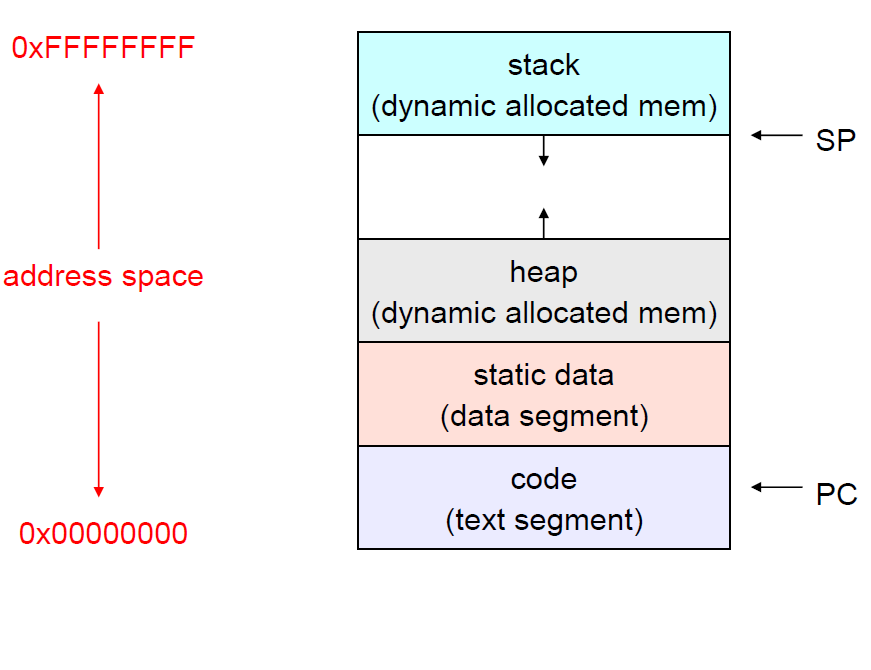

이전에도 많이 봐왔겠지만 아래의 그림은 프로세스가 사용하는 address space가 됩니다.

위의 주소 공간들이 MMU를 통해서 실제 DRAM의 Physical address로 변환되게 되는 것 입니다.

여기서 stack과 heap은 늘어나고 줄어들 수 있는 공간입니다. 그래서 Dynamic allocated mem이라고 하는 것 입니다.

위는 Virtual memory와 Physical memory에 각자 로딩이 되어 mapping되는 것 입니다.

Swapping기법을 사용한다면 Page 0부터 Page X까지의 공간이 Physical memory 공간에 순서대로 들어가야 하지만

Paging기법을 사용하게 되면 Paging과 frame의 사이즈를 맞춘 상태로 순서에 상관없이 Physical memory에 로딩되는 것 입니다.

위의 그림은 Paging에 대한 것으로 각 virtual page는 4K단위로 나뉘어져 있는 것 입니다. 64K이므로 총 15개의 page를 가집니다.

Physical memory 마찬가지로 virtual page와 같은 크기를 가져야하기 때문에 4K단위로 총 8개의 Page를 가지게 됩니다.

위는 4K단위로 쪼개져 있기 때문에 세부적인 주소를 알고싶다면, 1024 단위 배수로 해당 블록에서의 세부 주소를 알 수 있습니다.

위의 그림을 통해서 예를 들자면, 만약에 $\text{MOV REG, 8196}$이 있다면, 8196은 Virtual address space의

8K - 12K영역에 있고, Physical memory address으로 mapping되어 있는 영역을 보면 24K-28K의 영역인 것을 알 수 있습니다.

8K - 12K의 시작 주소는 $1024*8 \; = \; 8192$가 되고, $8196-8192 \; = \; 4$이기 때문에 8192로 부터 4Byte위에

있는 위치이고, $1024*24 \; = \; 24576$이기 때문에 $24576*4 \; = \; 24580$의 Physical memory address에

mapping되어 있는것 입니다. 여기서 1024씩 곱한 것은 $2^{10}\text{(1K)} \; = \; 1024$이기 때문입니다. 단위는 Byte입니다.

Virtual page가 Physical memory어디에 저장되어 있는지에 대한 정보는 모두 Page table에 있습니다.

또한 위에서 virtual page에서 'X'로 표시되어 있는 것들은 변환하려는 정보가 없기 때문에 없는 page들은 Disk에 있고

Disk에서 가져와야 합니다. 이런 상황들을 Page fault라고 부릅니다.

Page fault가 발생하면 OS routine으로 가고 Blocked로 처리하게 되고 Physical memory address에서 안쓰는 영역을

없애고 Disk에서 가지고 할당해주게 됩니다.

그리고 Page fault가 해결되고 난 이후에 Disk에서 가져오는 I/O가 처리되고 나면 X에 해당하는 Instruction을

다시 restart해줍니다. unmmaped page는 Disk에 있다는 것은 기억하시고 가면 좋습니다.

예전에 배웠던 process가 running하다가 page fault가 발생해서 blocked 되는 상황이 위의 상황이라고 보시면 됩니다.

위는 $\text{MOV REG, 8196}$은 $\text{MOV REG, 24580}$으로 변환되는 과정입니다.

$\text{MOV REG, 8196}$명령어는 위의 그림에서 16bit으로 incoming virtual address입니다.

또한 여기서 상위 4bit은 해당 page가 어디에 해당하는지를 나타내는 것 입니다. 그 아래 하위 12bit은 offset과 관련된 것 입니다.

그리고 상위 4bit에 해당하는 2는 2번째 page table index를 의미하는 것이고,

2번째 page table index는 Page Frame Number인 $110_{2}$가 Physical address의 상위 4bit이 되는 것 입니다.

위의 과정을 전체적으로 보면 아래의 그림과 같아집니다.

결국 Physical address는 memory bus에 실려서 Physical memory에 가게 되는 것 입니다.

여기서 Process가 CPU를 사용하고 있다는 것은 MMU에 Page table이 들어가 있다는 것 입니다.

Context switch가 일어나게 된다면 다른 process의 page table을 가지고 와야 하는 것 입니다.

page table을 가져온다는 이유는 page table은 DRAM에 저장되어 있기 때문입니다.

위의 그림에서 Page table Ptr(pointer)이 지금까지 없었지만 갑자기 그림에서 나타난게 궁금하신 분들이 있으실 것 입니다.

Page table Ptr은 PA(Physical address)가 들어있게 됩니다. 왜냐하면 Virtual address라면 나중에 계속해서 변환해줘야

하기 때문인데, Page table Ptr은 OS가 setting할 때 PA를 넣어주게 됩니다. Context switching이 일어날 때 setting해주고

Page table의 시작주소가 Page table Ptr에 넣어주게 되는 것 입니다.

PTE(Page Table Entry)의 구조는 아래와 같습니다.

1. Present/absent(valid bit)

해당 page가 현재 유효한지 여부를 나타내는 것으로 페이지가 현재 Physical memory에 존재하는지 여부에 따라 접근 가능한지

아닌지를 나타냅니다.

2. reference bit

페이지가 최근에 참조되었는지 여부를 나타내는 bit으로 최근에 참조된 적이 있는지 아닌지에 대한 여부를 나타냅니다.

3. modify bit(dirty)

해당 page가 수정되었는지 여부를 추적하는 bit입니다. page가 수정된 상태로 디스크에 있는 원본과 다르다면 '1' 같다면

'0' 입니다.

4. protection bit

page에 대한 접근 권한을 지정하는 bit으로 읽기, 쓰기, 실행 권한을 나타내게 됩니다.

instruction이 배치된 page는 write를 허용안하고 execution이 허용되고, data가 배치된 page는 write는 허용이 되고

execution은 허용되지 않습니다.

5. caching disabled

hardware cache의 bit이 '1'이 setting이 되어있다면 해당 page를 access할 때 cache로 access시키지 않게 되는 것 입니다.

예를 들어서 STUR이나 LDUR과 같은 instruction으로 memory에 접근한 다음에 데이터를 가져올 때 cache에 가지고 오는데,

해당 bit이 '1'로 설정되어 있다면 cache에 access시키지 않는다는 것을 의미합니다.

지금까지 paging에 대해서 알아봤는데, paging의 장점은 무엇이 있을까요?

1. 메모리 관리하기 쉽다.

loading되는 단위가 다 page단위이기 때문에 external fragmentation이 없습니다.

하지만 page를 꽉 채워서 사용하지 않을 수 있기 때문에 internal fragmentation은 존재하게 됩니다.

2. page를 Disk에 보내더라도 정해진 사이즈로 보내기 때문에 쉽게 보낼 수 있습니다.

이는 I/O성능과 관련되어 있습니다.

3. 전체 page를 Physical memory에 넣을 필요가 없기 때문에 공간을 효율적으로 사용할 수 있습니다.

그럼 Paging의 단점은 없을까요?

답을 말하자면 그렇지 않고 단점은 존재합니다.

1. interanl fragmentation이 존재합니다.

2. memory로 access하기 위해서 page table에 access해야 하기 때문에 memory에 한번 더 access해야 합니다.

물론 이 단점은 TLB라는 caching을 사용해서 해결할 수 있습니다.

3. page table이 크기 때문에 큰 용량을 사용하게 된다는 단점이 있습니다.

page table도 memory 영역을 사용하기 때문에 크다는 것은 단점이 될 수 있습니다.

위에서 page table을 access해야 하기 때문에 memory를 두 번 access해야 한다는 단점이 있기 때문에 이를 해결하기 위해서

TLB를 사용한다고 했으니 이에 대해서 한번 살펴보도록 하겠습니다.

TLB(Translation Lookaside Buffer)는 위의 문제를 해결하기 위한 방법입니다.

TLB는 fully associative cache구조를 사용하고 있는데, miss가 발생한다면

memory 또는 Disk에 갔다와야 하기 때문에 많은 오버헤드가 발생하기 때문입니다.

그렇다면 cache의 구성과 함께 cache의 내부 구성과 내보내는 값은 어떻게 될까요?

cache의 tag는 virtual page number를 사용하고 cache의 value는 PTE가 나오게 됩니다.

또한 MMU에서 PTE + offset으로 직접 계산해서 PA를 내보내게 됩니다.

위는 TLB의 구조입니다.

위에서 TLB의 기본에 대해서 배워봤으니 TLB에서 관리되거나 알아야 할 것들은 무엇이 있을지 알아보고 마무리하겠습니다.

만약에 위에서 TLB가 miss가 계속 발생하게되는 주소가 있다면 page table에 해당 주소를

TLB에 가지고 와야합니다. 이때 TLB가 다 차있다면 공간을 만들기 위해 특정한 내용을 없애고 넣어줘야 하기 때문에

LRU(Least Recently Used)를 사용해서 없애주고 그 주소의 값을 넣어줘야 합니다.

그렇게 가지고 온 값을 계속해서 사용하다가 miss가 발생해서 새로운 정보로 대체되어야 하거나 OS가 update할 때 consistency 문제가 발생해서 이 문제를 일치 시켜줘야 할 때, Page table의 정보를 바꿔줘야 합니다. Page table의 정보를 바꿔주기 위해서는 Page table이 최신 정보인지 아닌지 판별해야 하는데, 이를 위해서 dirty bit을 사용해서 Page table의 값이 최신 정보와 다른지 같은지 판별할 수 있게 되는 것 입니다.

여기까지 알아보고 이후에 추가되는 부분이 있다면 글을 수정해서 정보를 수정하도록 하겠습니다.

글 읽어주셔서 감사합니다.

'전자전기공학 > 운영체제' 카테고리의 다른 글

| [Operating System/운영체제][Inverted page table, Page replacement algorithm] (0) | 2024.11.06 |

|---|---|

| [Operating System/운영체제][TLB, Multilevel page table] (0) | 2024.11.03 |

| [Operating System/운영체제][memory관리, Bit Map, Linked List, Fragmentation] (4) | 2024.10.28 |

| [Operating System/운영체제][Synchronization] (0) | 2024.10.14 |

| [Operating System/운영체제][Thread] (4) | 2024.10.08 |